Note that the counter resets to 0 when the active-low reset becomes 0, and when reset is de-asserted at around 150ns, the counter starts counting from the next occurence of the positive edge of clock. Hence, initially the o/ps are Q 3 Q 2 Q 1 Q 0 0000.

Initially, a short negative going pulse is applied to the clear input of all flip-flops. Since 4-bit counter is required we will use 4 J-K flip-flops. The flip-flop used for the asynchronous counter is negative edge-triggered flip-flops. That is, if 0 is given as the input, 1 is produced at the output and vice versa. In other words, this flip-flop produces complementing output. Because the output toggles in T flip-flop.

4 BIT DOWN COUNTER WITH EDGE TRIGGERED FLIP FLOP CODE

Simulation complete via $finish(1) at time 170 NS + 0 Design 4-bit Johnson Counter using JK flip-flop. Here is the code for 4 bit Synchronous UP counter.The module uses positive edge triggered JK flip flops for the counter.The counter has also a reset input.The JK flipflop code used is from my previous blog.For simulating this counter code,copy and paste the JK flipflop code available at the above link in a file and store the file in the same directory with other. For the design of the asynchronous counter, T flip-flops are used. Initialize testbench variables to 0 at start of simulation This initial block forms the stimulus of the testbench If reset is 1, then design should be allowed to count up, so increment counter Once inside this block, it checks if the reset is 0, if yes then change out to zero This always block will be triggered at the rising edge of clk (0->1) Output reg out) // Declare 4-bit output port to get the counter values Input rstn, // Declare input port for reset to allow the counter to be reset to 0 when required Module counter ( input clk, // Declare input port for clock to allow counter to count up Clock pulses are fed into the CK input of FF0 whose output, Q 0 provides the 2 0 output for FF1 after one CK pulse. There is a 4-bit output called out which essentially provides the counter values. 5.6.1 shows a 4 bit asynchronous up counter built from four positive edge triggered D type flip-flops connected in toggle mode. An active-low reset is one where the design is reset when the value of the reset pin is 0. The design contains two inputs one for the clock and another for an active-low reset. When counter is at a maximum value of 4'b1111 and gets one more count request, the counter tries to reach 5'b10000 but since it can support only 4-bits, the MSB will be discarded resulting in 0.

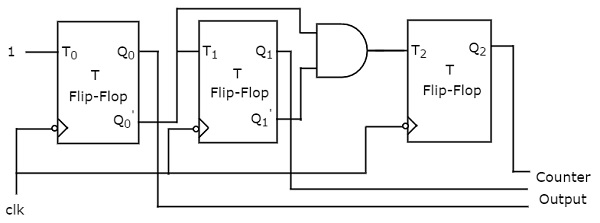

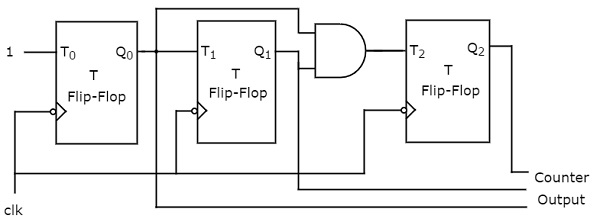

The rollover happens when the most significant bit of the final addition gets discarded. It will keep counting as long as it is provided with a running clock and reset is held high. Positive edge-triggered flip-flop (b) (ii) T-flip-flop (c) (iii) Clocked flip-flop with clear an preset (d) (iv) Negative level triggered. The 4-bit counter starts incrementing from 4'b0000 to 4'h1111 and then rolls over back to 4'b0000. Consider a 3-bit counter, designed using T flip-flop, as shown below: Assuming the initial state of the counter given by PQR as 000, what are the next three states.